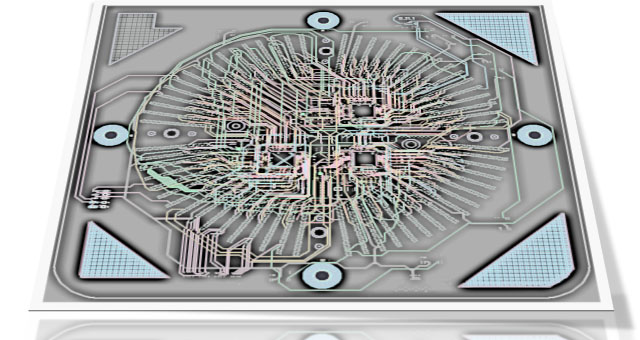

半導体テスターボードの基板設計品となります。

同等の回路構成が3DUT分あり、繰り返し回路のように同じ配置、配線にコピーできるが機構的な制限があり各DUT毎にそのすべてを変える必要がありました。DUTの位置の都合上、スペースに制約があり配置に苦労した設計品でした。

POGO部への接続は任意のため、アサイン先を作業者が選択。それによりアサイン先の制約や条件も考慮する必要があり、間違いが無いよう細心の注意をはらいました。

また、POGO部の配置は円弧を描くような配置により、角度が一定でないので慣れるまで時間を費やしたテスターボードです。数多くのテスターボードの設計経験があるとはいえ、難易度の高い設計品となりました。

- 基板層数:26層

- 480×480mm

- VIA:貫通

- 部品点数:251点

- 部品ピン数:7,282ピン

- 実装:両面

- 設計期間:約2.5週間

- 3DUT品(176ピン)

- CAD:Allegro